U Galileo traduce libro y crea simulador sobre arquitectura de computadoras RISC-V

Universidad Galileo, en colaboración con los autores David Patterson (Premio Nobel de Computación, Turing) y Adrew Waterman, traduce al español el libro The RISC V Reader, y crea simulador de procesador basado en el libro, al que todas las personas tendrán acceso gratuito para aprender y expandir su conocimiento en alta tecnología.

La traducción del libro RISC-V fue gracias a la relación interinstitucional que mantiene Universidad Galileo, con Universidad de Berkeley, quien confió junto con los autores del libro, David Patterson y Adrew Waterman, en el trabajo profesional de esta casa de estudios, y su manejo en temas de investigación científica y desarrollo tecnológico de alto nivel.

“El libro RISC-V es una introducción concisa y referencia, para programadores de sistemas embebidos, estudiantes, e interesados en una arquitectura moderna, popular y abierta. RISC-V abarca desde los microcontroladores embebidos más baratos de 32 bits hasta las computadoras más rápidas de 64 bits en la nube.”

En este texto se muestra cómo RISC-V se basó en la arquitectura del pasado aplicando mejoras en errores encontrados.

Entre algunas de las características del contenido del libro se destacan:

• Introduce el set de instrucciones RISC-V en tan solo 100 páginas, incluyendo 75 figuras

• Una Tarjeta de Referencia de RISC-V de 2 páginas que resume todas las instrucciones

• Un Glosario de Instrucciones de 50 páginas que define todas las instrucciones detalladamente

• 75 resaltadores de buen diseño de arquitectura mediante el uso de íconos al margen

• 50 barras laterales con comentarios interesantes e historia de RISC-V

• 25 citas para transmitir la sabiduría de científicos e ingenieros reconocidos

RISC-V es la quinta versión de la especificación RISC

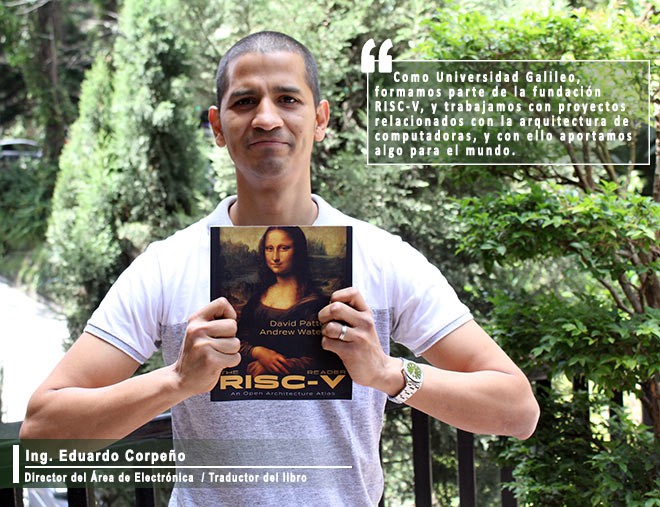

RISC es una filosofía de arquitectura de computadoras que surgió en los ´80s, para ampliar más sobre esta versión, el Ing. Eduardo Corpeño, Director del Área de Electrónica en Universidad Galileo, y uno de los traductores Libro The RISC V Reader, explicó: “Hoy la Fundación RISC-V está a cargo de esta quinta versión de la arquitectura RISC, y tiene muchas compañías que están a bordo, y lo que quiere es proporcionar una alternativa a los procesadores actuales, principalmente para aplicaciones embebidas que pertenecen a la arquitectura llamada –ARM- que es una compañía que desde hace mucho tiempo adopto la filosofía RISC, y que la encontramos en la mayoría de los aparatos y aplicaciones embebidas. Un detalle interesante es que RISC-V es una arquitectura abierta, esto quiere decir que tiene código abierto, por lo que el objetivo es permitir que el desarrollo de la arquitectura se lleve a cabo de una forma moderada por la fundación, y que no tenga intereses comerciales”.

Así también enfatizó: “Como Universidad Galileo, formamos parte de la fundación RISC-V y estamos trabajando con proyectos relacionados con la arquitectura para aportar algo al mundo”.

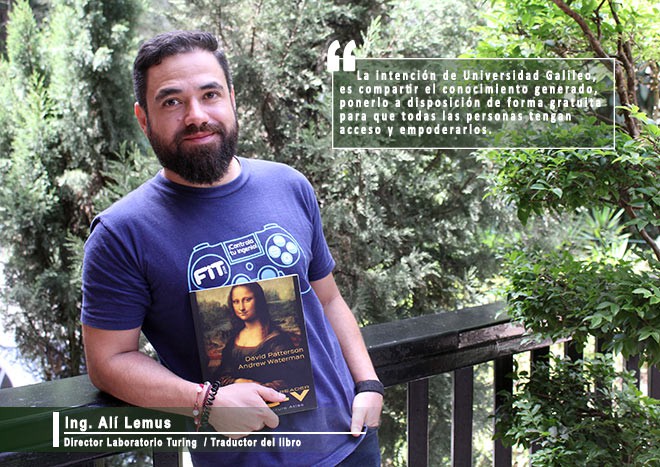

El Ing. Alí Lemus, Director del Laboratorio Turing y traductor del Libro, explicó que el concepto de RISC-V es importante debido a que “Quiere ser como el nuevo Linux, de las arquitecturas de las computadoras, y de los nuevos procesadores, Permite agregarle al procesador ciertas extensiones que tiene RISC-V ya predefinidas”.

«El libro se publicó en Barcelona el mismo día en inglés y en español, creemos fervientemente en la educación, y en empoderar a las personas, este trabajo colaborativo nos permitió tener un buen nivel de trabajo y nos dio la oportunidad de hacer algo por el mundo, darles a todas las personas acceso a que ellos puedan tener herramientas para que puedan crecer por sí mismos«.

A lo que también resaltó: “En Universidad Galileo y en Universidad de Berkeley, creemos esto va a cambiar el mundo a nivel de microprocesadores que es la tecnología fundamental que operan las computadoras de ahora”.

Simulador VSim

A raíz de la traducción del texto, se generó la idea de desarrollar un simulador de procesador, al que se pudiera tener acceso gratuito para el apoyo en clases de arquitectura u organización de computadoras.

El simulador VSim, se puede encontrar (open source) se puede utilizar de manera gratuita. Una de las ventajas de VSim, es que debido a que no existen muchos hardware RISC-V el simulador permitirá tener acceso a un hardware como tal.

En el, se podrá explorar un procesador a lo interno, y encontrar donde se encuentran los registros y la memoria.

Uno de los ingenieros a cargo del desarrollo del VSim es el Ing. Andrés Castellanos, quien trabaja para el Laboratorio Turing, el profesional explicó una de las razones que lo motivó a crear el simulador al respecto dijo: “El aspecto teórico es fundamental, pero en el lado de la academia, es importante la parte práctica, es por ello que decidí crear un simulador ensamblador de RISC –V, que acompañará el trabajo que realizaron en la traducción del libro. La cualidad de este es que permitirá utilizarlo y explorar cosas de un procesador que en la vida real no se puede, estas cosas son importantes dentro de la curva de aprendizaje de los estudiantes”.

Por: Msc. Cesar Martínez, Área de Comunicación Web